Визуализация и анализ под воздействием электронного пучка

Сканирующий электронный микроскоп (СЭМ, англ. SEM – Scanning Electron Microscope) является стандартным инструментом анализа дефектов интегральных схем (ИС, англ. IC – Integral Circuit). Обладая хорошей глубиной резкости, улучшенными возможностями по отображению рельефа поверхности, значительным рабочим расстоянием и чрезвычайно большим диапазоном увеличений по сравнению со световой микроскопией, СЭМ обеспечивает еще и уникальные методы визуализации и анализа ИС под воздействием электронного пучка.

Методы СЭМ, использующие инжекцию заряда для анализа ИС:

- EBIC (Electron Beam Induced Current) – метод регистрации тока, индуцированного электронным пучком;

- RCI (Resistive Contrast Imaging) – визуализация резистивного контраста;

- CIVA, LECIVA (Charge-Induced Voltage Alteration) – метод регистрации заряда, индуцированного изменением напряжения (как высокой так и низкой энергии).

Визуализация тока, индуцированного электронным пучком (EBIC)

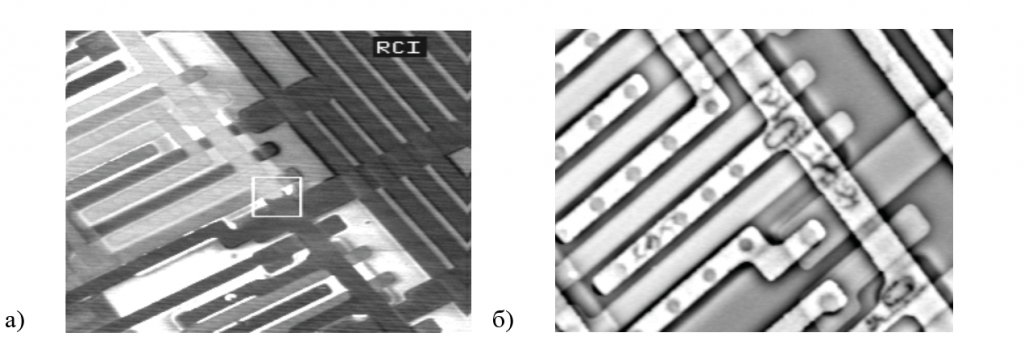

EBIC предназначен для локализации уровня Ферми в исследуемых областях. Метод позволяет оценить характеристики полупроводниковых материалов и преимущественно используется для идентификации скрытых утечек и дефектов в кремнии (Si). Пример визуализации EBIC показан на рисунке 1 (диффузии видны по всей ИС).

Рисунок 1 – Пример изображения EBIC всего кристалла

Визуализация резистивного контраста (RCI)

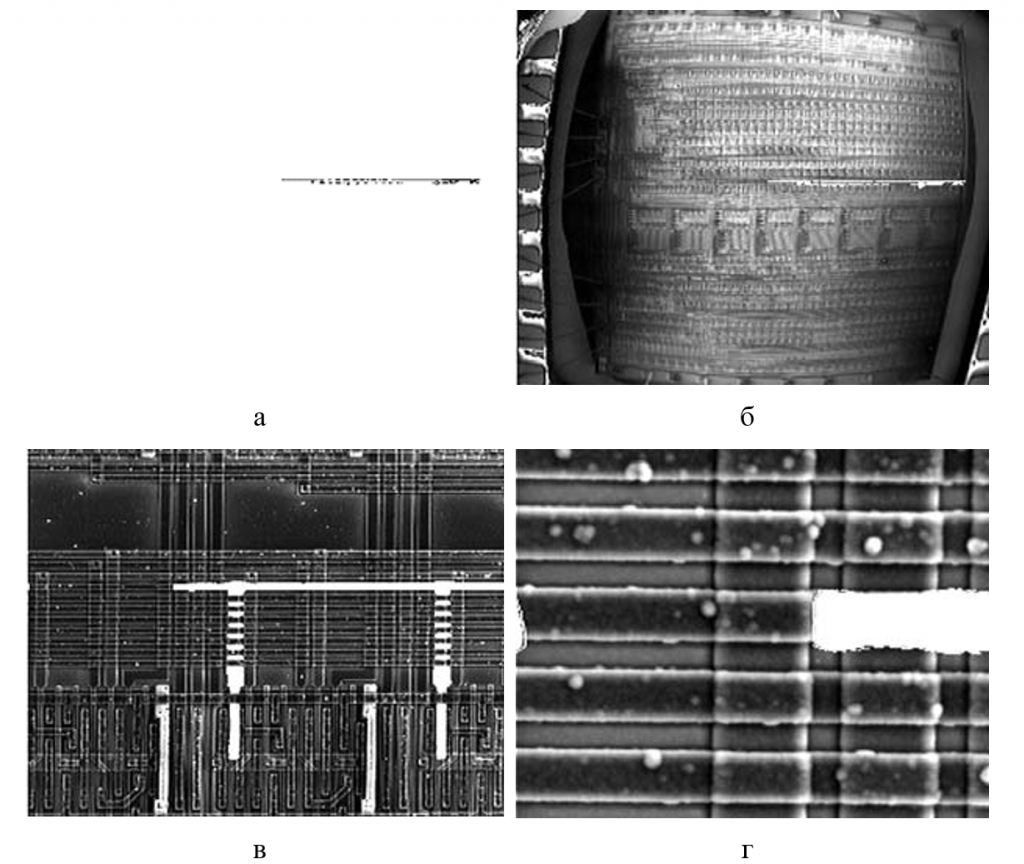

Метод RCI позволяет сформировать карту относительных сопротивлений между двумя тестовыми узлами запассивированной ИС. Сформированная карта будет отображать скрытые проводники ИС и может использоваться для локализации дефектов проводников микросхемы.

Рисунок 2 – а) Пример визуализации RCI локализации разорванного проводника;

б) BSE-изображение той же самой области, демонстрирующее образование повреждений (микротрещин) в металлизации

Визуализация изменений напряжения, вызванных зарядом (CIVA)

Метод визуализации изменений напряжения, вызванных зарядом (Charge-Induced Voltage Alteration, CIVA) был разработан для обнаружения разрывов металлических дорожек КМОП ИС, с пассивацией или без нее. CIVA позволяет визуализировать разрывы межсоединений ИС в виде изображения. Также CIVA может быть успешно использован при тестировании аналоговых биполярных ИС.

Рисунок 3 – Изображение CIVA, сохраненное при малом увеличении (а),

совмещенное с изображением образца во вторичных электронах (б), и

изображения CIVA / SE с более высокими увеличениями, позволяющими локализовать дефект (в, г)

Изменения напряжения, вызванные зарядом, при низких энергиях первичного пучка (LECIVA)

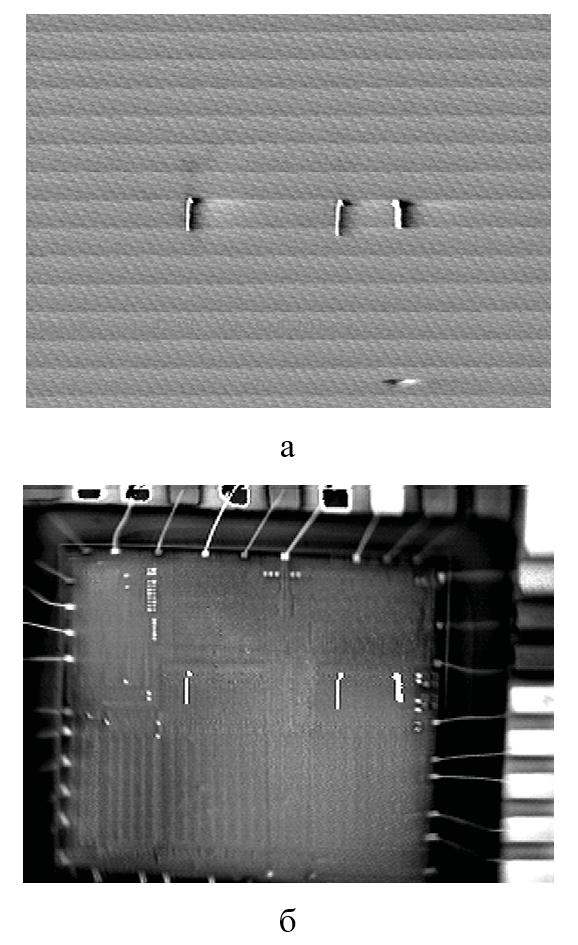

Использование метода CIVA при низких энергиях первичного электронного пучка (<1,0 кэВ) позволяет идентифицировать дефекты металлических проводников типа разрыв под слоем пассивации аналогично традиционному методу CIVA. Основное различие CIVA с низкой энергией пучка (Low Energy Charge-Induced Voltage Alteration, LECIVA) от традиционного метода состоит в том, что первый из них оказывает гораздо более бережное воздействие на тестируемую ИС. Кроме того, LECIVA может быть реализована на базе электронно-лучевых систем, которые функционируют только при низких энергиях первичного электронного пучка. В первую очередь следует применять низкоэнергетическую CIVA из-за практически полного отсутствия разрушающего воздействия на образец.

Изображения поврежденных проводников, полученные методом LECIVA при энергии электронного пучка 300 эВ, показаны на рисунке 4.

Рисунок 4 – Изображение LECIVA, полученное при энергии электронного пучка 300 эВ,

на котором можно заметить 3 проводника с разрывами (а). Для упрощения восприятия приведено

изображение, на котором результаты LECIVA наложены поверх изображения образца,

выполненного во вторичных электронах (б).

Вывод

Представленные методики позволяют проводить исследования материалов и структур. Развитие электроники и стремительное уменьшение размеров технологической нормы не препятствует применению данных методик для анализа отказов современных устройств. Все представленные методы позволяют получить хорошую картину для качественной оценки и являются отличными инструментами в развитии исследовательской базы.

При подготовке статьи были использованы следующие материалы:

-

“Semicondactor Reliability Handbook” Renesas Electronics Rev 2.50 Jan 2017;

-

J. Ross “Microelectronics Failure Analysis Desc Reference. Sixth Edition” USA: ASM International, 2011 г. – 660 стр.